का डिज़ाइनफोटोनिकएकीकृत परिपथ

फोटोनिक एकीकृत परिपथइंटरफेरोमीटर या पथ की लंबाई के प्रति संवेदनशील अन्य अनुप्रयोगों में पथ की लंबाई के महत्व के कारण (पीआईसी) को अक्सर गणितीय स्क्रिप्ट की मदद से डिजाइन किया जाता है।चित्रफोटोमास्क का निर्माण एक वेफर पर कई परतों (आमतौर पर 10 से 30) को पैटर्न करके किया जाता है, जो कई बहुभुजीय आकृतियों से बनी होती हैं, जिन्हें अक्सर GDSII प्रारूप में दर्शाया जाता है। फोटोमास्क निर्माता को फ़ाइल भेजने से पहले, डिज़ाइन की शुद्धता को सत्यापित करने के लिए PIC का सिमुलेशन करना अत्यंत आवश्यक है। सिमुलेशन को कई स्तरों में विभाजित किया गया है: सबसे निचला स्तर त्रि-आयामी विद्युत चुम्बकीय (EM) सिमुलेशन है, जहाँ सिमुलेशन उप-तरंगदैर्ध्य स्तर पर किया जाता है, हालाँकि सामग्री में परमाणुओं के बीच की अंतःक्रियाओं को स्थूल पैमाने पर नियंत्रित किया जाता है। विशिष्ट विधियों में त्रि-आयामी परिमित-अंतर समय-डोमेन (3D FDTD) और आइगनमोड विस्तार (EME) शामिल हैं। ये विधियाँ सबसे सटीक हैं, लेकिन संपूर्ण PIC सिमुलेशन समय के लिए अव्यावहारिक हैं। अगला स्तर 2.5-आयामी EM सिमुलेशन है, जैसे परिमित-अंतर बीम प्रसार (FD-BPM)। ये विधियाँ बहुत तेज़ हैं, लेकिन सटीकता में कुछ कमी आती है और ये केवल समानांतर प्रसार को ही संभाल सकती हैं और इनका उपयोग अनुनादकों के अनुकरण के लिए नहीं किया जा सकता है। अगला स्तर 2D EM सिमुलेशन है, जैसे 2D FDTD और 2D BPM। ये भी तेज़ हैं, लेकिन इनकी कार्यक्षमता सीमित है, जैसे कि ये ध्रुवीकरण रोटेटर का अनुकरण नहीं कर सकतीं। एक और स्तर संचरण और/या प्रकीर्णन मैट्रिक्स सिमुलेशन है। प्रत्येक प्रमुख घटक को इनपुट और आउटपुट वाले घटक में बदल दिया जाता है, और जुड़े हुए वेवगाइड को एक चरण शिफ्ट और क्षीणन तत्व में बदल दिया जाता है। ये सिमुलेशन अत्यंत तेज़ होते हैं। आउटपुट सिग्नल संचरण मैट्रिक्स को इनपुट सिग्नल से गुणा करके प्राप्त किया जाता है। प्रकीर्णन मैट्रिक्स (जिसके तत्वों को S-पैरामीटर कहा जाता है) घटक के एक तरफ इनपुट और आउटपुट सिग्नल को गुणा करके दूसरी तरफ इनपुट और आउटपुट सिग्नल ज्ञात करता है। मूल रूप से, प्रकीर्णन मैट्रिक्स में तत्व के भीतर परावर्तन होता है। प्रकीर्णन मैट्रिक्स आमतौर पर प्रत्येक आयाम में संचरण मैट्रिक्स से दोगुना बड़ा होता है। संक्षेप में, 3डी ईएम से लेकर ट्रांसमिशन/स्कैटरिंग मैट्रिक्स सिमुलेशन तक, सिमुलेशन की प्रत्येक परत गति और सटीकता के बीच एक संतुलन प्रस्तुत करती है, और डिजाइनर डिजाइन सत्यापन प्रक्रिया को अनुकूलित करने के लिए अपनी विशिष्ट आवश्यकताओं के लिए सिमुलेशन का सही स्तर चुनते हैं।

हालांकि, कुछ तत्वों के विद्युत चुम्बकीय सिमुलेशन पर निर्भर रहना और संपूर्ण पीआईसी का सिमुलेशन करने के लिए स्कैटरिंग/ट्रांसफर मैट्रिक्स का उपयोग करना फ्लो प्लेट के सामने पूरी तरह से सही डिज़ाइन की गारंटी नहीं देता है। उदाहरण के लिए, गलत गणना की गई पथ लंबाई, उच्च-क्रम मोड को प्रभावी ढंग से दबाने में विफल रहने वाले मल्टीमोड वेवगाइड, या एक-दूसरे के बहुत करीब स्थित दो वेवगाइड जिनके कारण अप्रत्याशित कपलिंग समस्याएं उत्पन्न होती हैं, सिमुलेशन के दौरान अनदेखे रह सकते हैं। इसलिए, हालांकि उन्नत सिमुलेशन उपकरण शक्तिशाली डिज़ाइन सत्यापन क्षमताएं प्रदान करते हैं, फिर भी डिज़ाइनर द्वारा उच्च स्तर की सतर्कता और सावधानीपूर्वक निरीक्षण, व्यावहारिक अनुभव और तकनीकी ज्ञान के साथ मिलकर, डिज़ाइन की सटीकता और विश्वसनीयता सुनिश्चित करने और फ्लो शीट के जोखिम को कम करने के लिए आवश्यक है।

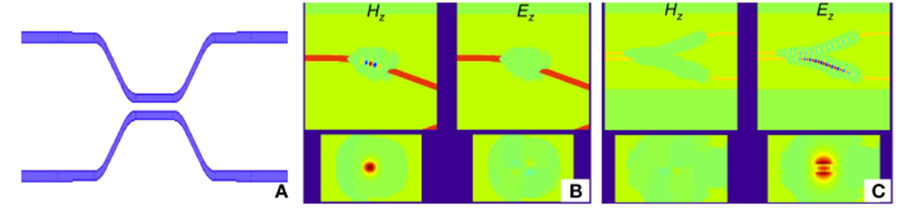

स्पार्स एफडीटीडी नामक तकनीक की मदद से किसी संपूर्ण पीआईसी डिज़ाइन पर सीधे 3डी और 2डी एफडीटीडी सिमुलेशन किए जा सकते हैं, जिससे डिज़ाइन का सत्यापन हो सके। हालांकि किसी भी विद्युत चुम्बकीय सिमुलेशन टूल के लिए बहुत बड़े पैमाने के पीआईसी का सिमुलेशन करना मुश्किल है, लेकिन स्पार्स एफडीटीडी एक अपेक्षाकृत बड़े स्थानीय क्षेत्र का सिमुलेशन करने में सक्षम है। पारंपरिक 3डी एफडीटीडी में, सिमुलेशन एक विशिष्ट क्वांटाइज्ड वॉल्यूम के भीतर विद्युत चुम्बकीय क्षेत्र के छह घटकों को आरंभ करके शुरू होता है। समय बीतने के साथ, वॉल्यूम में नए क्षेत्र घटक की गणना की जाती है, और इसी तरह प्रक्रिया चलती रहती है। प्रत्येक चरण में बहुत सारी गणनाएँ करनी पड़ती हैं, इसलिए इसमें लंबा समय लगता है। स्पार्स 3डी एफडीटीडी में, वॉल्यूम के प्रत्येक बिंदु पर प्रत्येक चरण में गणना करने के बजाय, क्षेत्र घटकों की एक सूची रखी जाती है जो सैद्धांतिक रूप से मनमाने ढंग से बड़े वॉल्यूम के अनुरूप हो सकती है और केवल उन्हीं घटकों के लिए गणना की जाती है। प्रत्येक समय चरण में, क्षेत्र घटकों से सटे बिंदुओं को जोड़ा जाता है, जबकि एक निश्चित शक्ति सीमा से नीचे के क्षेत्र घटकों को हटा दिया जाता है। कुछ संरचनाओं के लिए, यह गणना पारंपरिक 3डी एफडीटीडी की तुलना में कई गुना तेज हो सकती है। हालांकि, विरल FDTDS विक्षेपण संरचनाओं से निपटने में अच्छा प्रदर्शन नहीं करते हैं क्योंकि यह समय क्षेत्र बहुत अधिक फैलता है, जिसके परिणामस्वरूप सूचियाँ बहुत लंबी और प्रबंधित करने में कठिन हो जाती हैं। चित्र 1 एक ध्रुवीकरण बीम स्प्लिटर (PBS) के समान 3D FDTD सिमुलेशन का एक उदाहरण स्क्रीनशॉट दिखाता है।

चित्र 1: 3डी स्पार्स एफडीटीडी से प्राप्त सिमुलेशन परिणाम। (ए) सिमुलेट की जा रही संरचना का शीर्ष दृश्य है, जो एक दिशात्मक कपलर है। (बी) क्वासी-टीई उत्तेजना का उपयोग करके किए गए सिमुलेशन का स्क्रीनशॉट दिखाता है। ऊपर दिए गए दो आरेख क्वासी-टीई और क्वासी-टीएम संकेतों का शीर्ष दृश्य दर्शाते हैं, और नीचे दिए गए दो आरेख संबंधित अनुप्रस्थ काट दृश्य दर्शाते हैं। (सी) क्वासी-टीएम उत्तेजना का उपयोग करके किए गए सिमुलेशन का स्क्रीनशॉट दिखाता है।

पोस्ट करने का समय: 23 जुलाई 2024